### AI-DRIVEN CO-OPTIMIZATION OF DESIGN & MANUFACTURING FOR HETEROGENEOUS AI CHIPS

Sung Kyu Lim Georgia Institute of Technology July 3, 2025 Korea-U.S. Forum on Nanotechnology

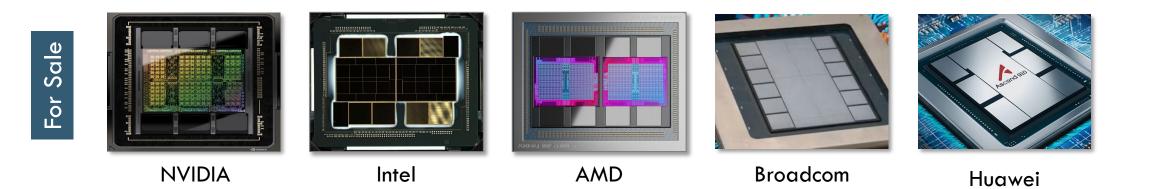

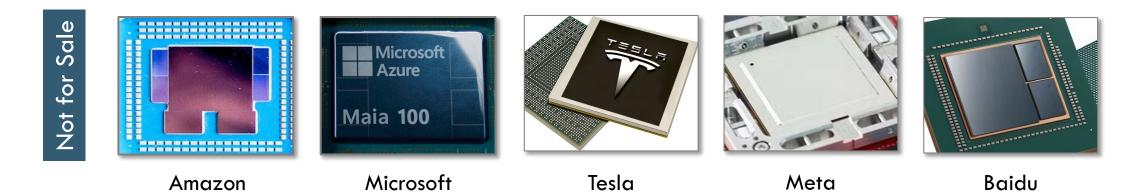

## **COMMERCIAL AI CHIPS: MULTI-CHIP PACKAGING**

### MAINSTREAM IN AI SERVICING

### **DESIGN-MANUFACTURING CO-OPTIMIZATION**

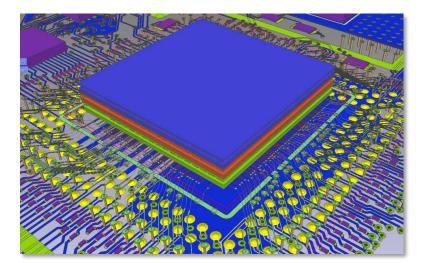

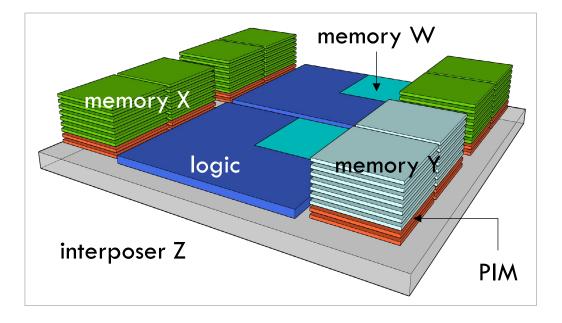

### Package Design

Package Manufacturing

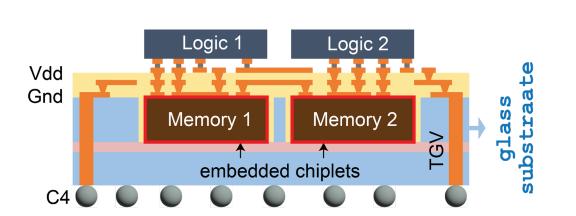

**Glass Substrate**

better insulation, better CTE, larger size, lower cost, die embedding

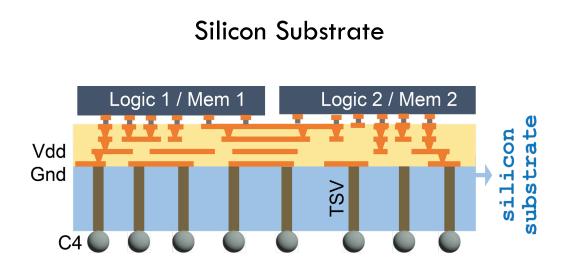

better thermal conductivity, finer pitch interconnect

OK, but what will they do to my chips?

## THREE WAYS TO ANSWER

Build Samples Most accurate but slowest & expensive

X

Design & Simulate X Accurate but

slow

## WHERE IS DATA?

2.5D IC design & simulation data Hard to find

I can't wait I will build them myself

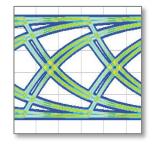

## STEP 1/6: WE NEED PDK

#### Manufacturing Samples

RDL via

embedded dies

**RDL** wires

through glass vias

### **PDK Parameters**

| Design Rules       |           |  |  |  |

|--------------------|-----------|--|--|--|

| Metal thickness    | 4um       |  |  |  |

| Wire width / space | 2um / 2um |  |  |  |

| Micro-bump pitch   | 35um      |  |  |  |

| Material Properties (AGC-EN-A1) |                   |      |  |  |

|---------------------------------|-------------------|------|--|--|

| substrate                       | Permittivity (Dk) | 4.9  |  |  |

|                                 | Young's mod (GPa) | 74.8 |  |  |

|                                 | CTE (ppm/K)       | 3.2  |  |  |

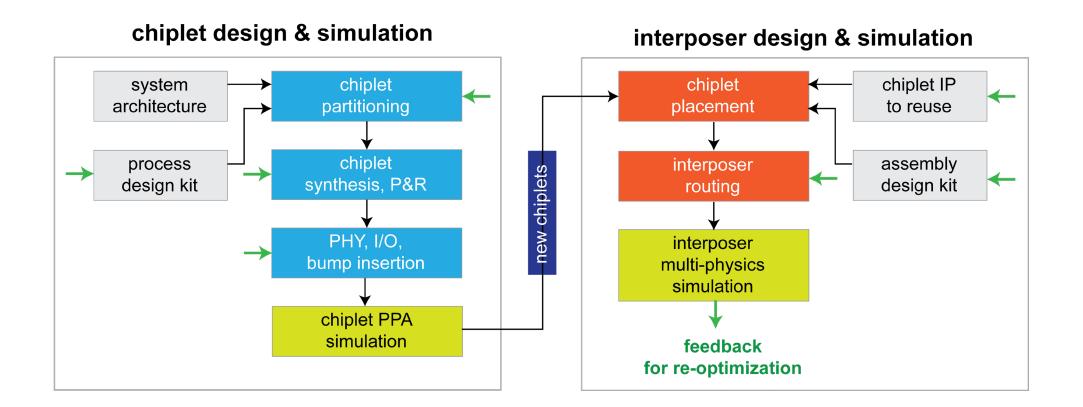

## **STEP 2/6: WE NEED DESIGN TOOLS**

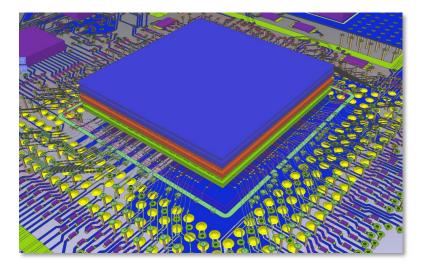

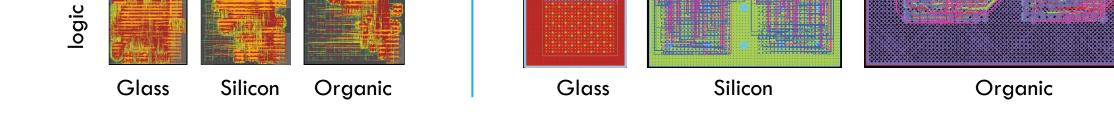

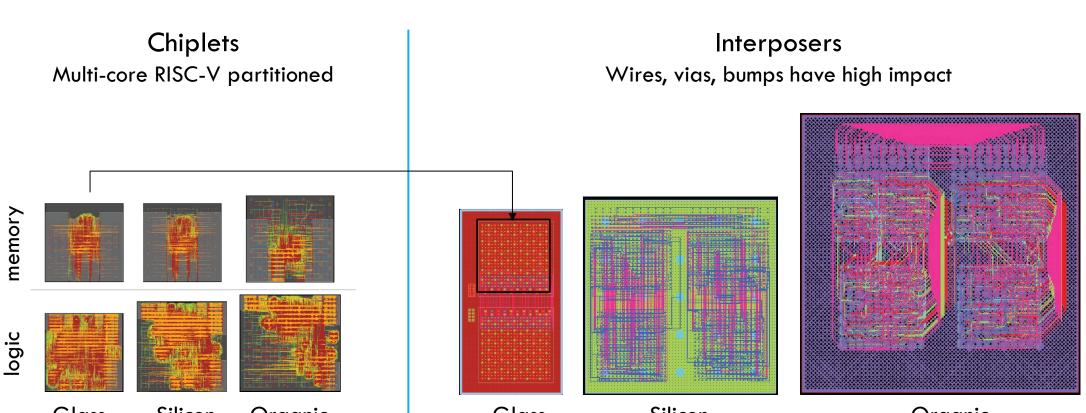

# STEP 3/6: WE DO DESIGN

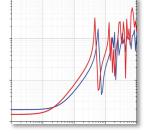

## STEP 4/6: WE DO SIMULATION

|             |                            | 2D   | Glass      | Silicon    | Glass<br>Benefit |

|-------------|----------------------------|------|------------|------------|------------------|

| Cost        | Area (mm²)                 | 2.56 | 1.87       | 4.84       | 2.6x             |

|             | Metal layer used           |      | 3          | 4          | 1.3x             |

|             | Interposer WL (mm)         |      | 37.9       | 937        | 24.7x            |

| Reliability | Eye width/height           |      | 1.4ns/0.8v | 1.0ns/0.4V | 1.4x             |

|             | PDN Impedance ( $\Omega$ ) | -    | 0.97       | 7.9        | 8.1x             |

|             | IVR Settling Time (us)     | -    | 3.7        | 4.1        | 1.1x             |

|             | Thermal (°C)               | -    | 27.5       | 23.3       | 0.8x             |

Eye diagram

PDN impedance

Thermal map

IR-drop map

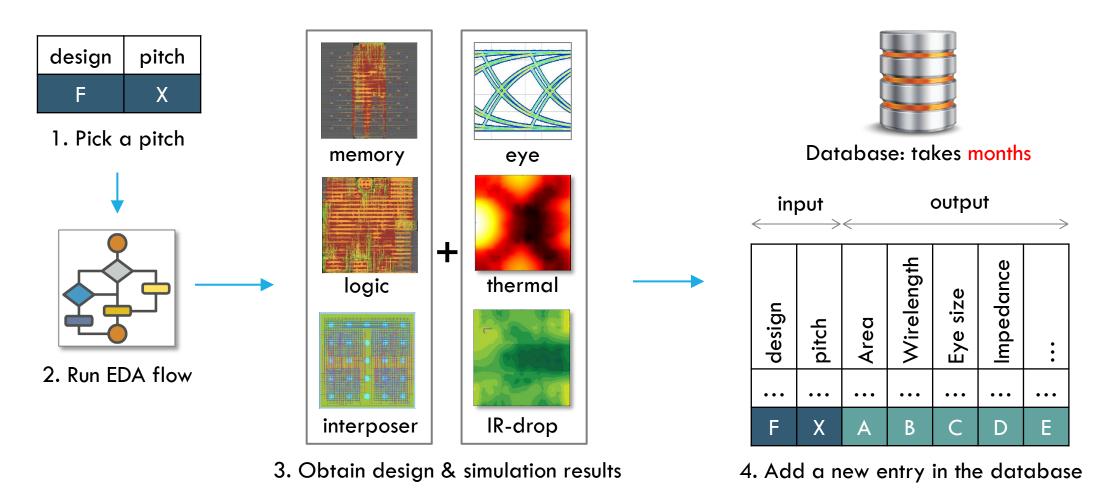

# STEP 5/6: WE BUILD DATASET

Seungmin Woo, et al, "AI-Driven Evaluation and Optimization of Bump Pitch Effects on Chiplet and Interposer Design Quality", IEEE Int. Conf. on Computer-Aided Design, 2024.

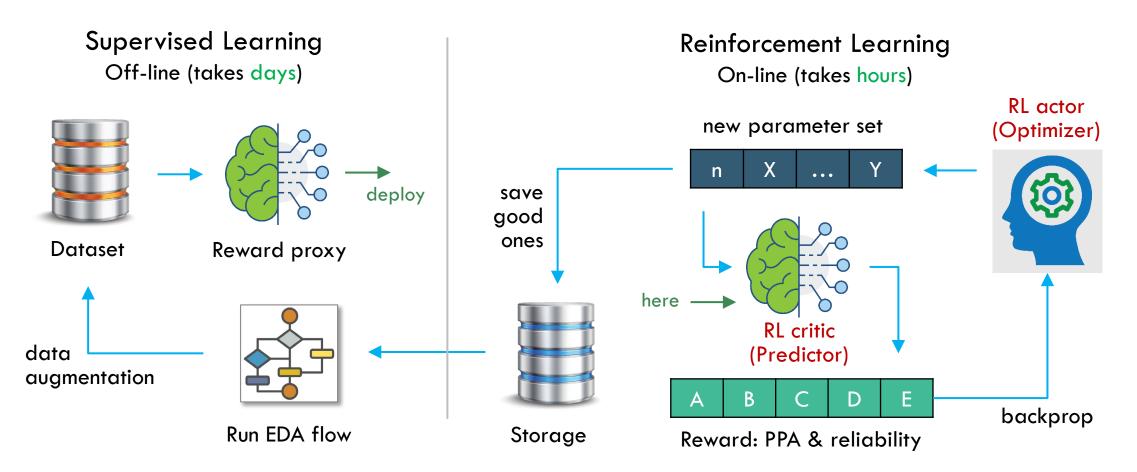

# STEP 6/6: WE TRAIN AI MODELS

## TWO THINGS WE ASK AI

#### Al Prediction (takes seconds)

Design quality of my chip?

| design metric                      | prediction | accuracy |

|------------------------------------|------------|----------|

| Interposer size (mm <sup>2</sup> ) | 2,300      | 99%      |

| Eye (ns/V)                         | 0.32/0.89  | 95%      |

| PDN impedance ( $\Omega$ )         | 6.8        | 95%      |

| Max temperature (°C)               | 28.0       | 99%      |

Best process recipes \_\_\_\_\_\_ for my chip?

Al Optimization

(takes hours)

## MORE IMPORTANT THAN EVER

Package Design

Package Manufacturing